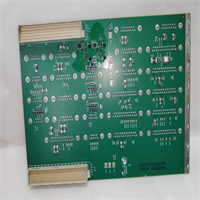

Description

Key Technical Specifications (Reconstructed from Industry Knowledge)

- Product Identifier: VMIC ASSY 11993R2

- Manufacturer: VMIC (Virtual Machine Instruments Corp.)

- Platform: VMEbus (likely 6U VME64 or VME64x compliant)

- Form Factor: Standard 6U VME board (233.35 mm × 160 mm)

- Likely Function: Custom FPGA-based I/O processor, MIL-STD-1553 interface, ARINC 429 controller, or real-time data concentrator

- Processor/Core Logic: Possibly Intel i960, PowerPC, or discrete FPGA (e.g., Xilinx XC4000/XC5200 series)

- Memory: Onboard SRAM or DRAM (estimated 4–32 MB); possibly battery-backed NVRAM

- I/O Interfaces: May include RS-422/485, discrete TTL/CMOS I/O, optical links, or military avionics buses

- Backplane Interface: Standard VME P1/P2 connectors (32-bit, A24/A32 addressing)

- Operating Environment: Designed for conduction-cooled or forced-air ruggedized chassis

- Software Dependency: Proprietary drivers, likely running under VxWorks or pSOS real-time OS

-

VMIC ASSY 11993R2

System Role and Downtime Impact

The VMIC ASSY 11993R2 typically serves as a specialized co-processor or protocol engine within larger VME-based embedded systems—common in radar signal processing, flight test instrumentation, satellite ground stations, or nuclear control systems. Due to its custom nature, it often handles timing-sensitive tasks (e.g., synchronized sampling, bus arbitration, or hardware handshaking) that cannot be replicated by generic replacements.

If this assembly fails, the host system usually experiences catastrophic functional loss, as the logic is deeply embedded in both hardware and application software. Reverse-engineering is exceptionally difficult without original schematics, FPGA bitstreams, or firmware images. In regulated industries (e.g., defense, energy), such failures can trigger compliance reviews or mission aborts.

Reliability Analysis and Common Failure Modes

Given its likely deployment era (mid-to-late 1990s), the 11993R2 is vulnerable to multiple age-related failure mechanisms:

- Electrolytic capacitor degradation on power rails → voltage droop or brownout resets

- Battery leakage from onboard NVRAM backup cells → PCB corrosion and trace damage

- FPGA configuration memory loss (if using volatile SRAM-based FPGAs) → boot failure

- VME edge connector oxidation → intermittent communication or bus errors

- Thermal fatigue in solder joints (especially under conduction-cooled mounting) → latent opens

A critical risk is the lack of self-diagnostics: most such assemblies predate standardized health monitoring, so faults are often discovered only during system-level anomalies.

Preventive maintenance recommendations include:

- Imaging firmware/FPGA bitstreams using legacy JTAG or PROM programmers (if accessible)

- Replacing onboard lithium batteries proactively (even if voltage appears normal)

- Cleaning VME edge fingers with contact enhancer every 12–18 months

- Storing spares in temperature/humidity-controlled environments with periodic power cycling

- Capturing functional I/O behavior via logic analyzers to support future emulation

-

VMIC ASSY 11993R2

Lifecycle Status and Migration Strategy

Emerson does not recognize the VMIC 11993R2 in any current product portfolio. No direct or indirect replacement exists. Secondary market availability is sporadic, with many listings lacking test data or revision verification (note the “R2” suffix—revision mismatches can cause incompatibility).

Short-term mitigation strategies:

- Engage specialized obsolescence management firms for board-level repair or component reballing

- Maintain at least two verified, matched spares (same revision and firmware)

- Develop a functional test bench to validate units before installation

Long-term migration paths:

- FPGA emulation: Recreate functionality on modern platforms like Xilinx Kintex Ultrascale+ or Intel Cyclone 10 GX using captured interface specs

- Form-fit-function replacement: Design a custom mezzanine or carrier card compatible with VPX, CompactPCI Serial, or PCIe

- System-level abstraction: Replace the entire VME subsystem with a real-time target (e.g., Speedgoat, NI PXIe + FlexRIO) running emulated logic in Simulink or LabVIEW FPGA

Due to the high integration depth, migration requires significant engineering investment—but is increasingly necessary to meet cybersecurity, reliability, and sustainment mandates, especially in defense applications governed by DoD Instruction 4140.01. Early functional decomposition and interface documentation are essential to de-risk future transitions.

Tel:

Tel:  Email:

Email:  WhatsApp:

WhatsApp: